OpenMPWで作るQPUの可能性

本投稿は「量子コンピュータ Advent Calendar 2022」の12日目の記事となります。

はじめに

みなさま、ご存じでしょうか?OpenMPWプログラムというものを!

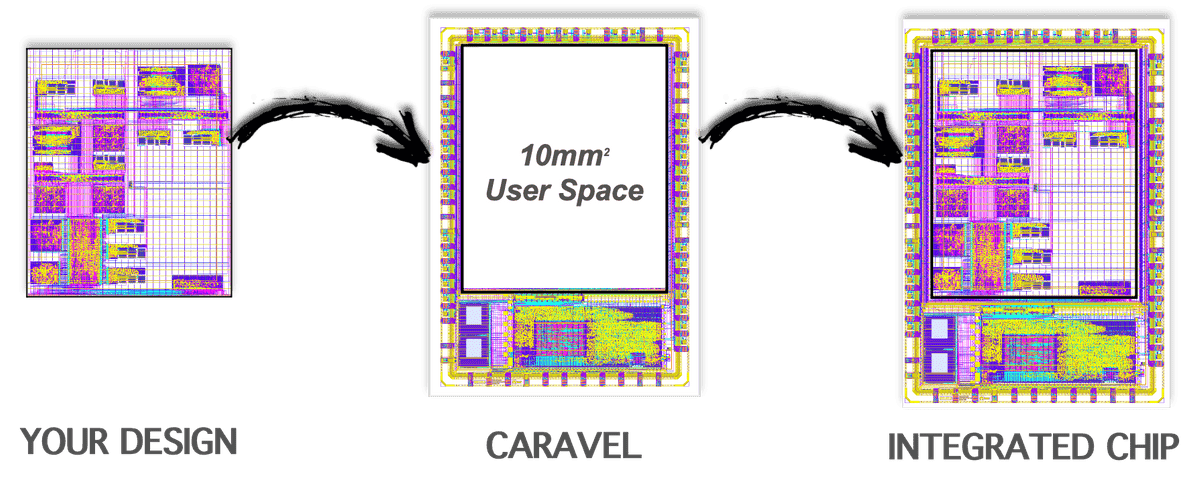

Google社が主催する無料で独自設計のASIC(シリコン)を作ることができるプログラムです!(公式サイト)細かいことは省いて、皆さんが気になるであろうことを表にすると下記のような感じです。

| 主催 | Google社 |

| ファブ | SkyWater Technology Foundry社 |

| プロセスルール | 130nm |

| レイヤー数 | 6層 |

| ユーザエリアサイズ | 10mm * 10mm |

| パッケージ | WCSP(Wafer-Level Chips Size Package) |

| 製造チップ数 | 300個 |

| 評価ボード(電源やデバッグ用ポートを装備) | 5枚 |

| シャトルタイミング | 偶数月に1回(40プロジェクトがランダムで採択) |

| 料金 | 無料(有料プラン有り) |

| ツール類 | 全てオープンソースソフトウェアとして公開 |

| 制限 | 製造した回路はオープンソースで公開する必要がある(有料プランでは不要) |

サイズはOK?

現在の最先端プロセスルールが「3~5nm」ですので、太古の昔のプロセスルールではありますが、研究レベルで試作されるQPUが90nmくらいを利用しております。さらに、ユーザエリアサイズが10mm x 10mmとなっており、4qubitのQPUが90nmで作った場合、10mm x 10mmサイズとなります。すなわち、2~4qubitのQPUを作るには十分なスペックといえるのではないでしょうか!(※来年にはSkyWater 90nmのシャトルも予定されています。余談ですがGlobalFoundries 180nmは2022/12にスタートしました。)

トランズモン素子はOK?

では、肝心のトランズモン素子を設計することはできるのでしょうか?一点懸念点はありますが、可能です!

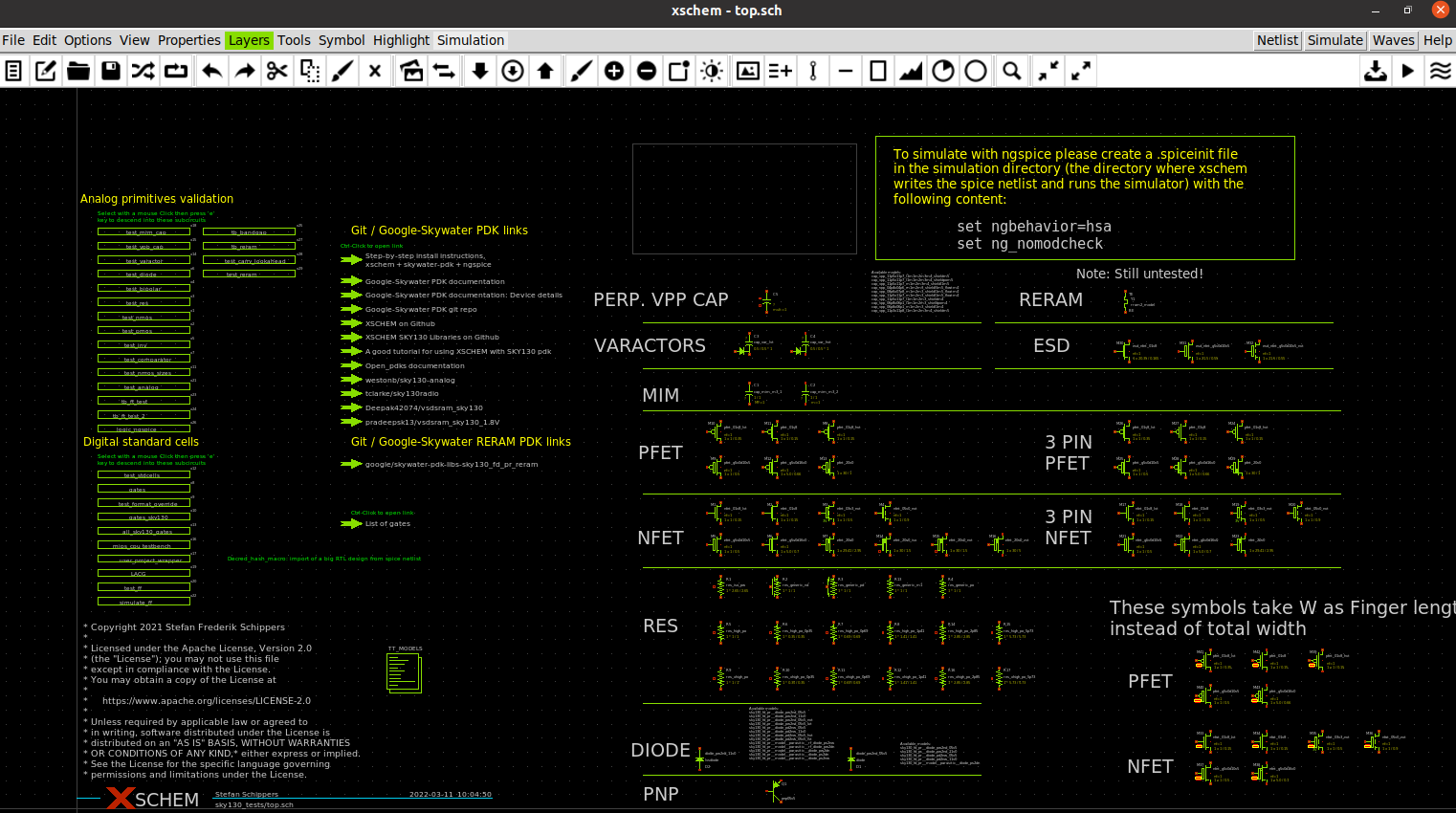

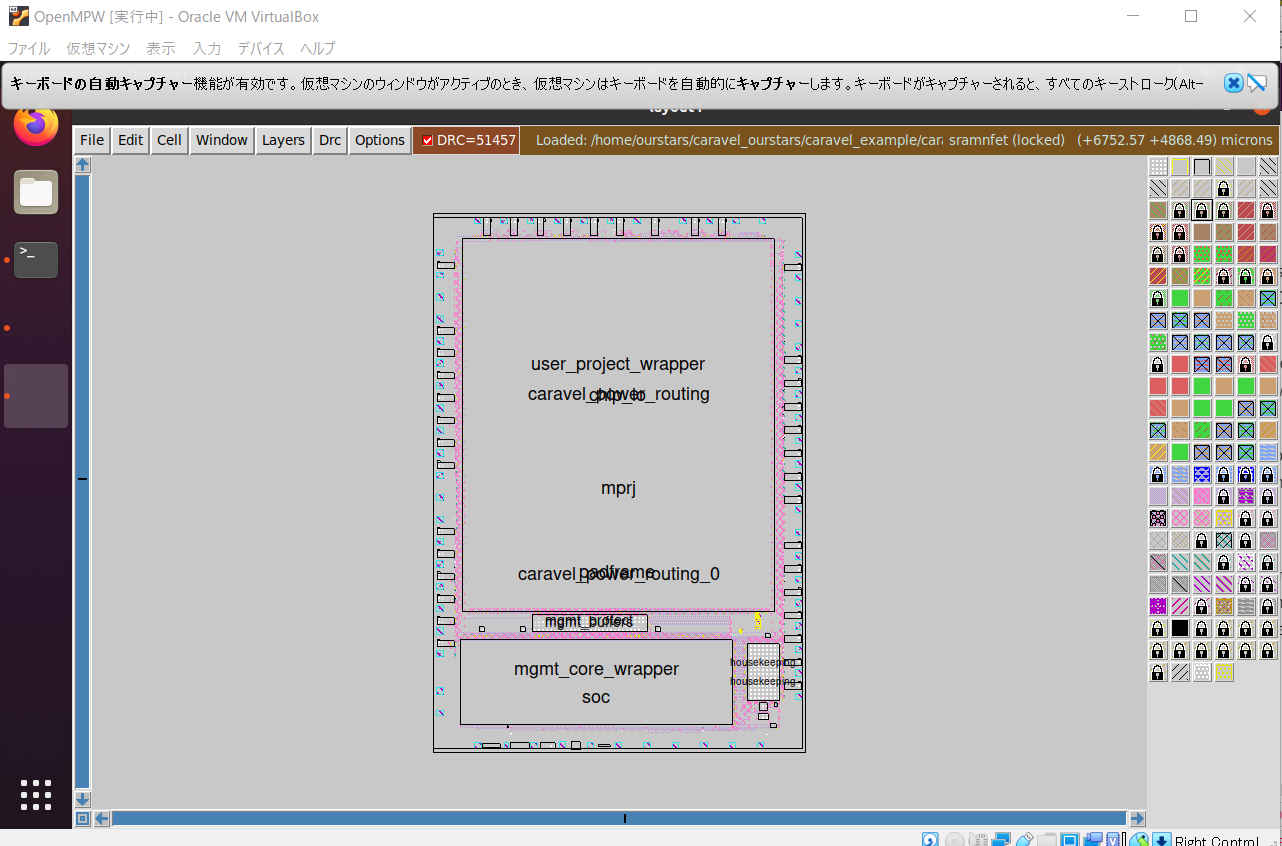

図2はアナログ回路のエディターで、PCB CADでいうところの回路図エディターです。これで、独自の素子や回路を作ることができます。ただ、数qubitであれば、図3のレイアウトエディターというPCB CADでいうところのPCBレイアウト(アートワーク)エディターで、作ってしまうほうが楽だと思います。(※アナログ回路でやる場合、PDKというライブラリをいじる必要が出る可能性があるためです)

そして、懸念点ですが、絶縁被膜などの厚さなどは調整できません。そのため、電圧を上げたりなどでうまく設計しないとトンネル効果を起こすことが難しい可能性があります。しかし「無料で2~3か月に一回」はシャトルがありますので、これを利用して何回も試行錯誤することでこの問題は解決できるのではないかと考えています。(※実際に、何度もバージョンを変えて出している方々もいます)

まとめ

ということで、簡単ではありましたが、自作QPUの可能性を感じていただけたのではないでしょうか?もし、我こそは!という方がいれば、ぜひチャレンジしてみてください!私のほうにお声がけいただければ、全力でサポートいたします!

その先はOK?

ただ、試作できたとしても、動作させるには希釈冷凍機を用意しないといけないので、そこが次のハードルとなりますが。。。あっ、コントローラは未踏の成果があるので、どうにかなります!(本投稿のQPUは「超電導量子コンピュータ向け」を想定しております)